## Kathir College of Engineering [Approved by AICTE | Affiliated to Anna University | Accredited by NAAC]

## Neelambur, Avinashi Road, Coimbatore-62

## SAMPLE QUESTION PAPER FOR CONTINUOUS ASSESSMENT

| Branch              | ECE | Sem.                       | III | Date |     | Duration | 90 min |

|---------------------|-----|----------------------------|-----|------|-----|----------|--------|

| Subject code & Name |     | EC8392 Digital Electronics |     |      | Max | k. Marks | 50     |

| Course Outcomes:                                                                                                                                      |       |       |       |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--|--|--|--|

| CO1 Relate mathematical concepts and digital fundamentals minimization techniques for logic optimization                                              | and d | apply | AP    |  |  |  |  |

| CO2 Analyse the specifications and design various combinational digital circuits using logic gates                                                    |       |       |       |  |  |  |  |

| CO3 Analyse the specifications and design various synchronous and asynchronous sequential circuits by successfully considering the constraints if any |       |       |       |  |  |  |  |

| CO4 Understand the concept of semiconductor memories and related<br>Technologies                                                                      |       |       |       |  |  |  |  |

| CO5 Understand essential logic families involved in the design of logic gates                                                                         |       |       |       |  |  |  |  |

| Part – A (07 x 02 = 14 Marks)                                                                                                                         | RBT   | со    | Marks |  |  |  |  |

| Answer All Questions                                                                                                                                  |       |       |       |  |  |  |  |

| 1 The solution to the quadratic equation $x^2$ -11x+22=0 is x=3 and x=6.                                                                              | U     | 1     | 2     |  |  |  |  |

| What is the base of the numbers?                                                                                                                      |       |       |       |  |  |  |  |

| 2 Show that A(B' + A · C')' can be implemented using only one 3-input AND gate                                                                        | AP    | 1     | 2     |  |  |  |  |

| 3 Implement the Boolean function $F(A,B,C) = \sum (1,5,7)$ using 8*1 MUX                                                                              | AP    | 2     | 2     |  |  |  |  |

| 4 Implement full adder's output functions using decoder                                                                                               | AP    | 2     | 2     |  |  |  |  |

| 5 Derive the excitation table of a JKFF from its characteristic table                                                                                 | AP    | 3     | 2     |  |  |  |  |

| and the characteristic equation                                                                                                                       |       |       |       |  |  |  |  |

| 6 Infer the term "Universal Shift register"                                                                                                           | U     | 3     | 2     |  |  |  |  |

| 7 Illustrate a 4-bit Switch-tail Ring Counter with the count sequence                                                                                 | U     | 3     | 2     |  |  |  |  |

| Part – B (02 x 10 = 20 Marks)                                                                                                                         | RBT   | СО    | Marks |  |  |  |  |

| Answer All Questions                                                                                                                                  |       |       |       |  |  |  |  |

| 8 (a) Simplify the following expression using the postulates and theorems                                                                             | AP    | 1     | 10    |  |  |  |  |

of Boolean algebra. Eliminate all group complements. Justify each step by stating or referring to the Boolean theorem or postulate you use. Don't skip any steps! **Do NOT use a Karnaugh map to simplify the expressions.**

$$F=(A \cdot B \cdot C)'(A + C)(A + C')$$

(OR)

8 (b) Simplify the following Boolean expressions, using four-variable AP 1 10 map:

AP

2

10

$$F(w,x,y,z) = x'z + w'xy' + w(x'y + xy')$$

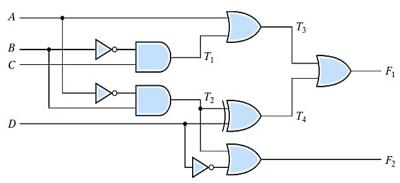

9 (a) Consider the combinational circuit shown in Fig.

- a) Derive the Boolean expressions for  $T_1$  through  $T_4$ . Evaluate the outputs  $F_1$  and  $F_2$  as a function of the four inputs.

- b) List the truth table with 16 binary combinations of the four input variables. Then list the binary values for  $T_1$  through  $T_4$  and outputs  $F_1$  and  $F_2$  in the table.

- a. Plot the output Boolean functions obtained in part (b) on maps and show that the simplified Boolean expressions are equivalent to the ones obtained in part (a).

(OR)

9 (b) Implement the following Boolean function with a 4 x 1 multiplexer AP 2 10 and external gates.

$$F(A, B, C, D) = \sum (1, 3, 4, 11, 12, 13, 14, 15)$$

Connect inputs A and B to the selection lines. The input requirements for the four data lines will be a function of variables C and D. These values are obtained by expressing F as a function of C and D for each of the four cases when AB = 00, 01, 10, and 11. These functions may have to be implemented with external gates.

## Part - C (01 x 16 = 16 Marks)

BT CO Marks

(To be framed to test Higher Order Thinking skills)

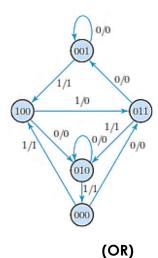

10 (a) A sequential circuit has three flip-flops A, B, C; one input x\_in; and AN 3 16 one output y\_out. The state diagram is shown in Fig. The circuit is to be designed by treating the unused states as don't-care conditions. Analyze the circuit obtained from the design to determine the effect of the unused states. Use JK flip-flops in the design

10 (b) A sequential circuit with two D flip-flops A and B, two inputs, x AN 3 16 and y; and one output z is specified by the following next-state and output equations

$$A(t + 1) = xy' + xB$$

$$B(t + 1) = xA + xB'$$

$$z = A$$

- (a) Draw the logic diagram of the circuit.

- (b) List the state table for the sequential circuit.

- (c) Draw the corresponding state diagram.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*